Research and development efforts in computing systems have recently shifted towards semiconductor memory technologies that not only complement the existing memory and storage hierarchy, but also reduce the distinction between memory (fast, expensive, volatile) and storage (slow, inexpensive, non-volatile). Part of our work focuses on the reliability and performance enhancement of NAND Flash memory in order to enable its employment in enterprise systems. However, although NAND Flash has already established itself in the memory and storage hierarchy between DRAM and HDDs, it still cannot serve as a universal memory/storage technology. There are various other solid-state technologies that promise to combine the performance benefits of semiconductor memories with the low cost of NAND Flash. These include ferroelectric, magnetic, phase-change, and resistive random-access memories. Of these, phase-change memory (PCM) is in the most advanced state of development today.

Our research group is working on various aspects of PCM technology, focusing on the enablement of MLC storage to make the technology more cost-competitive, as well as on the system-level exploitation of this new memory.

Phase-change memory

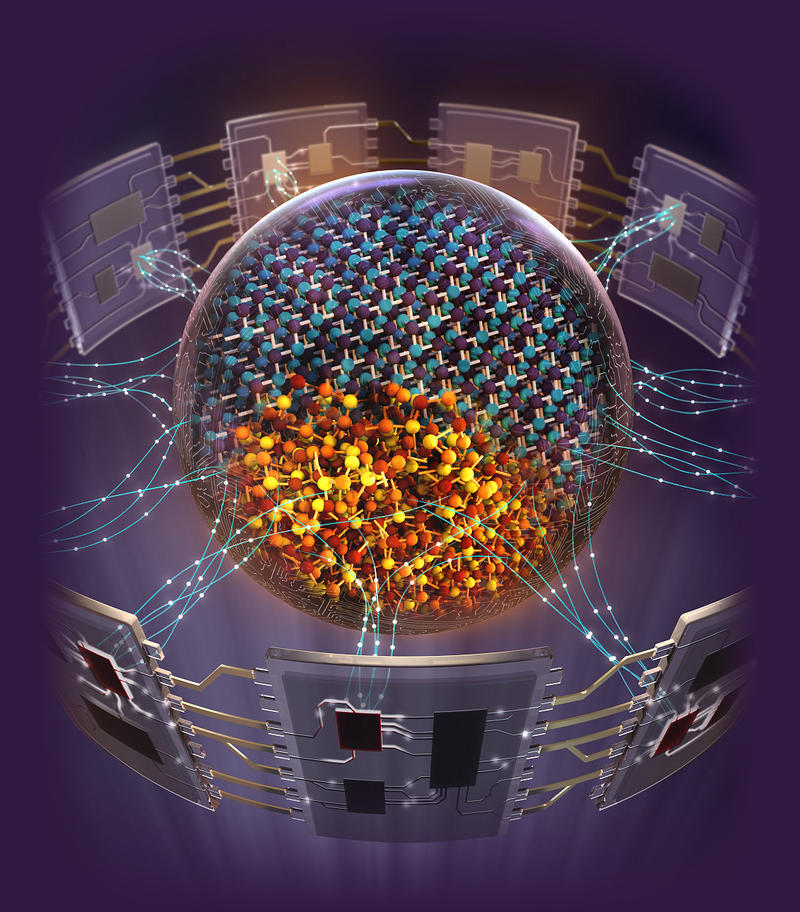

Phase-change memory (PCM) scores well in terms of most of the desirable attributes of a universal memory technology. In particular, it exhibits very good endurance on the order of 1 million cycles or more, moderate retention, and superb scalability to sub-20-nm nodes and beyond. In addition, it is amenable to multilevel-cell storage, thanks to the large resistivity contrast between its SET and RESET states. However, a number of technological challenges need to be addressed for PCM to become universal memory. A significant challenge of PCM technology is a phenomenon known as (short-term) resistance drift: The resistance of a cell is observed to drift upwards in time, with the amorphous state drifting more than its crystalline counterpart. Drift seriously affects the reliability of multilevel-cell (MLC) storage in PCM because of the reduced sensing margin between adjacent tightly-packed resistance levels. Therefore, effective solutions of the drift issue are a key factor for the cost competitiveness of PCM technology [ More ].

We are conducting research into iterative programming schemes, data readout metrics that are resilient to drift, as well as advanced signal processing and coding schemes to improve reliability by means of enabling higher storage capacity, longer data retention and higher endurance [ More ]. Our research on memory reliability enhancement has led to the successful demonstration of reliable 2 bits/cell storage and long data retention in large arrays of PCM cells after they have been cycled 1 million times [ More ]. We have recently demonstrated experimentally the successful storage and retention of 3 bits/cell data on PCM cell arrays that have been pre-cycled 1 million times and have also undergone environmental stress, with long exposure to high temperatures up to 80°C [ More ].

This is the first time such levels of reliability have been reached with Multi-bit PCM cell arrays, proving the viability of PCM technology for demanding enterprise (hybrid) memory applications.

Phase-change memory exploitation

At the system level, we are developing PCM-based storage subsystems that are connected to the host over the PCI-e bus. In a research prototypeco-developed with the University of Patras, Greece, the PCM chips are connected to custom-designed PCM channel controllers and attached to a mezzanine card, which in turn is attached to an FPGA board [15].

Recently, again in collaboration with the University of Patras, we have developed a second-generation PCM-based storage subsystem. In this version, a PCM DIMM (based on legacy PCM chips) is connected to a POWER8(R) processor through the PCI-e bus, and data exchange is performed over the Coherent Accelerator Processor Interface (CAPI).

This technology leverages the low latency and small access granularity of PCM, the efficiency of the OpenPOWER architecture and the CAPI protocol.

Access times below 5 µs can be achieved with a very high degree of consistency, even in random accesses. These results were presented recently at the OpenPOWER Summits in San Jose, California, and Barcelona, Spain.

The goal of this project is eventually to integrate PCM at a cluster and data center level using low-latency networking and appropriate support from system software, thereby enabling new use cases for data-intensive applications.

We envision stand-alone as well as hybrid applications that combine PCM and flash storage, with PCM as an extremely fast cache.

In the enterprise space, entire databases could be stored in PCM for blazing fast query processing for time-critical online applications, such as financial transactions.

Related links

- IBM Scientists Achieve Storage Memory Breakthrough, IBM press release

- IBM Scientists Achieve Storage Memory Breakthrough, YouTube video

- Hold the DRAM phone: IBM claims phase-change breakthrough, The Register

- IBM chip boffins mix phase-change-flash cocktail: Voila! SUPER fast memory card, The Register

- Low Latency Access to Phase Change Memory in OpenPOWER Systems, Open Power Foundation

- IBM demonstrates next-gen phase-change memory that’s up to 275 times faster than your SSD, Extreme Tech

- Multi-level-cell PCMs last for 10 million cycles, EE Times

- Made In IBM Labs: IBM Scientists Demonstrate Computer Memory Breakthrough, TheStreet

- SK Hynix and IBM Sign Joint Development for PCRAM, TechPowerUp

- Phase Change Memory - Altered States, The Economist

Publications

[1]

IEEE J. Emerging and Selected Topics in Circuits and Systems 6(1), 87-100, 2016.

[2] G.W. Burr, M.J. Brightsky, A. Sebastian, H.-Y. Cheng, J.-W. Wu, S. Kim, N.E. Sosa. N. Papandreou, H.-L. Lung, H. Pozidis, E. Eleftheriou, C.H. Lam,

“Recent Progress in Phase-Change Memory Technology,”

IEEE J. Emerging and Selected Topics in Circuits and Systems 6(2), 146-162, 2016.

[3] M. Stanisavljevic, H. Pozidis, A. Athmanathan, N. Papandreou, T. Mittelholzer, E. Eleftheriou,

“Demonstration of Reliable Triple-Level-Cell (TLC) Phase-Change Memory,”

in Proc. Int’l Memory Workshop, Paris, France, pp. 97-100, 2016.

[4] A. Prodromakis, N. Papandreou, E. Bougioukou, U. Egger, N. Toulgaridis, T. Antonakopoulos, H. Pozidis, E. Eleftheriou,

“Controller architecture for low-latency access to phase-change memory in OpenPOWER systems,”

in Proc. 26th Int’l Conference on Field Programmable Logic and Applications (FPL), 2016.

[5] A. Sebastian, M. Le Gallo, W. Koelmans, N. Papandreou, H. Pozidis, E. Eleftheriou,

“Multi-level storage in phase-change memory devices,”

in Proc. European Symposium on Phase Change and Ovonic Science (E\PCOS), 2016.

[6] M. Stanisavljevic, A. Athmanathan, N. Papandreou, H. Pozidis, E. Eleftheriou,

“Phase-change memory: Feasibility of reliable multilevel-cell storage and retention at elevated temperatures,”

in Proc. 2015 IEEE Int’l Symposium on Reliability Physics Symposium (IRPS), pp. 5B-6, 2015.

[7] A. Sebastian, D. Krebs, M. Le Gallo, H. Pozidis, E. Eleftheriou,

“A collective relaxation model for resistance drift in phase change memory cells,”

in Proc. 2015 IEEE Int’l Symposium on Reliability Physics Symposium (IRPS), pp. MY-5, 2015.

[8] A. Athmanathan, D. Krebs, A. Sebastian, M. Le Gallo, H. Pozidis, E. Eleftheriou,

“A finite-element thermoelectric model for phase-change memory devices,”

in Proc. 2015 Int’l Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 289-292, 2015.

[9] J. Cheon, I. Lee, C. Ahn, M. Stanisavljevic, A. Athmanathan, N. Papandreou, H. Pozidis, E. Eleftheriou, M. Shin, T. Kim, J.H. Kang,

“Non-resistance metric based read scheme for multi-level PCRAM in 25 nm technology,”

in Proc. 2015 IEEE Custom Integrated Circuits Conference (CICC), pp. 1-4, 2015.

[10] H. Pozidis, T. Mittelholzer, N. Papandreou, T. Parnell, M. Stanisavljevic,

“Phase Change Memory Reliability: A Signal Processing and Coding Perspective,”

IEEE Transactions on Magnetics 51(4), 1-7, 2015.

[11] A. Sebastian, M. Le Gallo, D. Krebs,

“Crystal growth within a phase change memory cell,”

Nature Communications 5, 2014.

[12] A. Athmanathan, M. Stanisavljevic, J. Cheon, S. Kang, C. Ahn, J. Yoon, M. Shin, T. Kim, N. Papandreou, H. Pozidis, E. Eleftheriou,

“A 6-bit drift-resilient readout scheme for multi-level phase-change memory,”

in Proc. 2014 IEEE Solid-State Circuits Conference (A-SSCC), 2014.

[13] D. Krebs, T. Bachmann, V.P. Jonnalagadda, L. Dellmann, S. Raoux, R. Spolenak,

“Changes in Electrical Transport and Density of States of Phase Change Materials Upon Resistance Drift,”

New J. Physics 16, 043015, 2014.

[14] D. Krebs, F. Zipoli, A. Sebastian, M. Le Gallo,

“Relaxation in Phase Change Memory Cells,”

in Proc. Spring Meeting of the Materials Research Society (MRS), San Francisco, CA, 2014.

[15] I. Koltsidas, P. Mueller, R. Pletka, T. Weigold, E. Eleftheriou, M. Varsamou, A. Ntalla, E. Bougioukou, A. Palli, T. Antonakopoulos,

“PSS: A prototype storage subsystem based on PCM,”

in Proc. 5th Non-Volatile Memories Workshop (NVMW) 2014.

[16] H. Pozidis, N. Papandreou, A. Sebastian, T. Mittelholzer, M.J. BrightSky, C.H. Lam, E. Eleftheriou,

“Reliable MLC Data Storage and Retention in Phase-Change Memory after Endurance Cycling,”

in Proc. Int’l Memory Workshop, Monterey, CA, pp. 100-103, 2013.

[17] J. Luckas, D. Krebs, S. Groth, J. Klomfass, R. Carius, C. Longeaud, M. Wuttig,

“Defects in Amorphous Phase-Change Materials,”

J. Materials Research 28(9), 1139-1147, 2013.

[18] G. Close, U. Frey, J. Morrish, R. Jordan, S. Lewis, T. Maffitt, M. Breitwisch, C. Hagleitner, C. Lam, E. Eleftheriou,

“A 256-Mcell Phase-Change Memory Chip Operating at 2+ bit/cell,”

IEEE Trans. Circuits and Systems 60(6), 1521-1533, 2013.

[19] D. Krebs, T. Bachmann, J.L.M. Oosthoek, V.P. Jonnalagadda, L. Dellmann, S. Raoux, J. Luckas, C. Longeaud, B.J. Kooi, R. Spolenak,

“Changes in Electrical Transport of Amorphous Phase Change Materials upon Annealing,”

in Proc. E¥PCOS 2013.

[20] A. Athmanathan, A. Sebastian, D. Krebs, M. Stanisavljevic, Y. Leblebici, E. Eleftheriou,

“Compact Electro-Thermal Model for Thermal Cross-Talk Analysis in PCM Arrays,”

in Proc. 2013 European Phase Change and Ovonics Symposium (EPCOS), 2013.

[21] H. Pozidis, N. Papandreou, A. Sebastian, T. Mittelholzer, M. Brightsky, C. Lam, E. Eleftheriou,

“A Framework for Reliability Assessment in Multilevel Phase-Change Memory,”

in Proc. IEEE Int’l Memory Workshop (IMW’2012), Milan, Italy, pp. 143-146, 2012.

[22] C. Longeaud, J. Luckas, D. Krebs,

“On the Density of States of Germanium Telluride,”

J. Applied Physics 112, 113714, 2012.

[23] J. L. M. Oosthoek, D. Krebs,

“The Influence of Resistance Drift on Measurements of the Activation Energy of Conduction for Phase-Change Material in Random Access Memory Line Cells,”

J. Applied Physics 112, 084506, 2012.

[24] D. Krebs,

“Impact of DoS Changes on Resistance Drift and Threshold Switching in Amorphous Phase Change Materials,”

J. Non-Crystalline Solids 358, 2412, 2012.

[25] N. Papandreou, H. Pozidis, A. Pantazi, A. Sebastian, M. Breitwisch, C. Lam, E. Eleftheriou,

“Programming Algorithms for Multilevel Phase-Change Memory,”

in Proc. IEEE Int’l Symposium on Circuits and Systems (ISCAS’2011), Rio de Janeiro, Brazil, pp. 329-332, 2011.

[26] N. Papandreou, H. Pozidis, T. Mittelholzer, G. Close, M. Breitwisch, C. Lam, E. Eleftheriou,

“Drift-tolerant Multilevel Phase-Change Memory,”

in Proc. IEEE Int’l Memory Workshop (IMW’2011), Monterrey, CA, pp. 147-150, 2011.

[27] G. Close, U. Frey, J. Morrish, R. Jordan, S. Lewis, T. Maffitt, M. Breitwisch, C. Hagleitner, C. Lam, E. Eleftheriou,

“A 512Mb Phase-Change Memory (PCM) in 90nm CMOS achieving 2b/cell,”

in Proc. Symp. VLSI Circuits 2011, Kyoto, Japan, 2011.

[28] N. Papandreou, A. Sebastian, A. Pantazi, M. Breitwisch, C. Lam, H. Pozidis, E. Eleftheriou,

“Drift-Resilient Cell-State Metric for Multilevel Phase-Change Memory,”

in Proc. 2011 IEEE Int’l Electron Devices Meeting (IEDM), pp. 3.5.1-3.5.4, 2011.

[29] H. Pozidis, N. Papandreou, A. Sebastian, A. Pantazi, T. Mittelholzer, G. F. Close, E. Eleftheriou,

“Enabling Technologies for Multilevel Phase-Change Memory,”

(invited)

in Proc. European Phase Change & Ovonics Symposium (E/PCOS), 2011.

[30] A. Athmanathan, G. F. Close,

“A 7-bit Readout Circuit in 90 nm CMOS for Drift-Resilient Multi-Level Phase-Change Memory,” (invited)

in Proc. European Phase Change & Ovonics Symposium (E/PCOS), 2011.

[31] D. Krebs,

“Impact of DoS Changes on Resistance Drift and Threshold Switching in Amorphous Phase Change Materials,”

European Phase Change & Ovonics Symposium (E/PCOS), 2011.

[32] A. Sebastian, N. Papandreou, A. Pantazi, H. Pozidis, E. Eleftheriou,

“Non-Resistance-Based Cell-State Metric for Phase-Change Memory,”

J. Appl. Phys. 110, 084505, 2011.

[33] J. Luckas, S. Kremers, D. Krebs,

“The Influence of a Temperature Dependent Bandgap on the Energy Scale of Modulated Photocurrent Experiments,”

J. Appl. Phys. 110, 013719, 2011.

[34] R. Haas, X.-Y. Hu, I. Koltsidas, R. Pletka,

“Subsystem and System-Level Implications of PCM,”

(invited)

in Proc. E\PCOS 2011, Zurich, Switzerland, pp. 158-166, 2011.

[35] N. Papandreou, A. Pantazi, A. Sebastian, E. Eleftheriou, M. Breitwisch, C. Lam, H. Pozidis,

“Estimation of Amorphous Fraction in Multilevel Phase-Change Memory Cells,”

Solid-State Electronics 54(9), 991-996, 2010.

[36] N. Papandreou, A. Pantazi, A. Sebastian, M. Breitwisch, C. Lam, H. Pozidis, E. Eleftheriou,

“Multilevel Phase-Change Memory,”

in Proc. IEEE Int’l Conference on Electronics, Circuits and Systems (ICECS’2010), Special Session on Nonvolatile Memories for Storage Applications, Athens, Greece, pp. 1025-1028, 2010.

[37] G. Close, U. Frey, M. Breitwisch, H. Lung, C. Lam, C. Hagleitner, E. Eleftheriou,

“Device, Circuit and System-Level Analysis of Noise in Multi-Bit Phase-Change Memory,”

in Proc. 2010 IEEE Int’l Electron Devices Meeting (IEDM), pp. 29.5.1-29.5.4, 2010.

[38] N. Papandreou, A. Pantazi, A. Sebastian, E. Eleftheriou, M. Breitwisch, C. Lam, H. Pozidis,

“Estimation of Amorphous Fraction in Multilevel Phase-Change Memory Cells,”

in Proc. European Solid-State Device Research Conference (ESSDERC’2009), Athens, Greece, pp. 209-212, 2009.

[39] A. Pantazi, A. Sebastian, N. Papandreou, M. Breitwisch, C. Lam, H. Pozidis, E. Eleftheriou,

“Multilevel Phase-Change Memory: Modeling and Experimental Characterization,”

(invited)

in Proc. European Phase Change and Ovonics Symposium (E\PCOS’2009), Aachen, Germany, pp. 34-41, 2009.

[40] D. Krebs, S. Raoux, C.T. Rettner, G.W. Burr, M. Salinga, M. Wuttig,

“Threshold Field of Phase Change Memory Materials Measured Using Phase Change Bridge Devices,”

Applied Physics Letters 95, 082101, 2009.